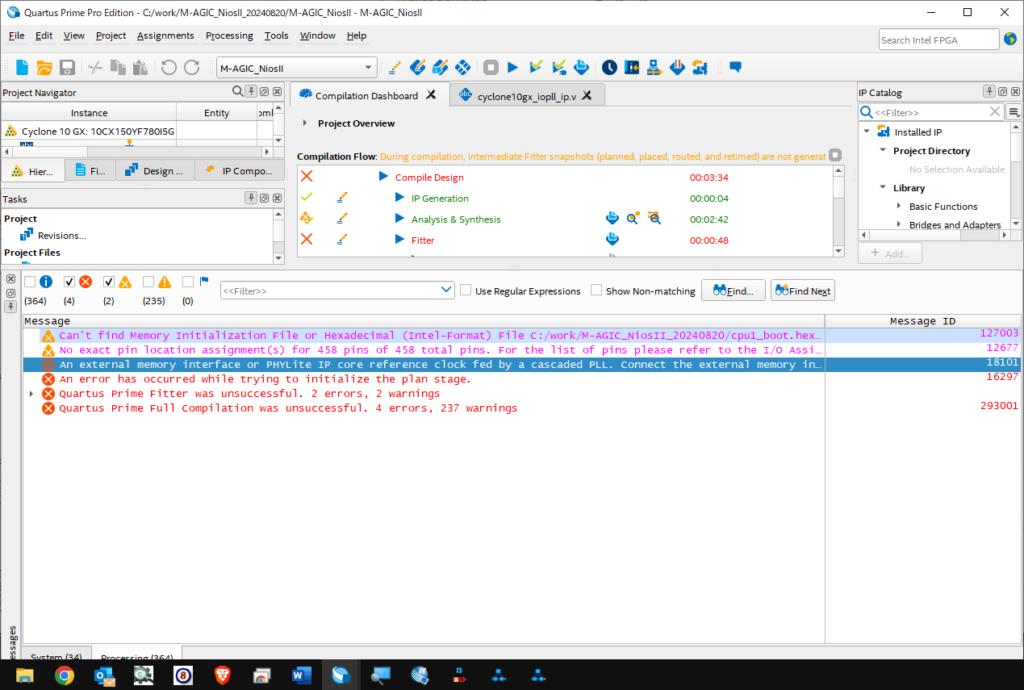

またQuartus Prime 20.1に怒られてしまった。

Error(18101): An external memory interface or PHYLite IP core reference clock fed by a cascaded PLL. Connect the external memory interface or PHYLite IP core reference clock to an input buffer.

どうやら、先輩の話ではQsys(Platform designer)で接続したDDR3LのIPへのクロック供給はPLLかませるとだめらしい。

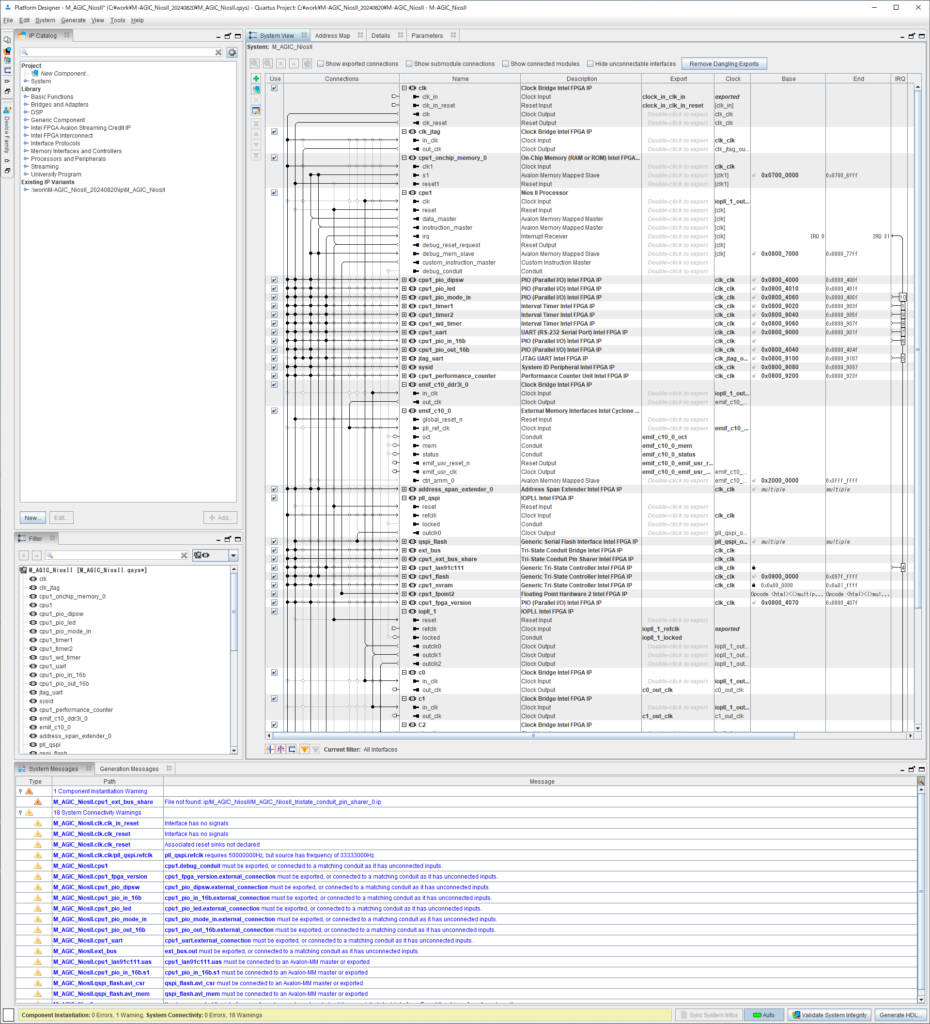

だめだったデザインがこれ↓

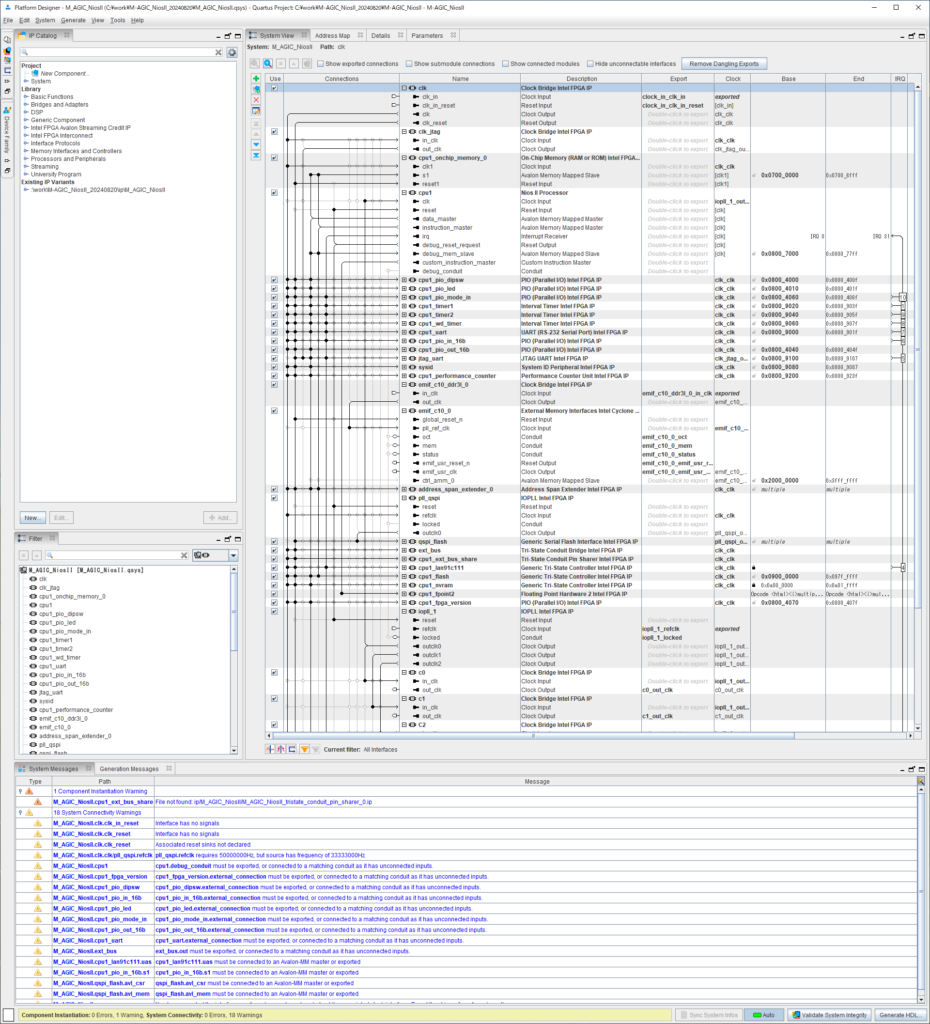

直したデザインがこれ↓

DDR3LのIPに供給してるクロックを外に出した。

変更後、ジェネレートして[_inst.v]をトップのVerilogに追記する。

とりあえずコンパイルが通るか確認するためにNiosIIの脚を全部外に出すだけのVerilog↓

/**************************************************************************/

/*** Specifications ***/

/*** ***/

/*** Project name :Niosii ***/

/*** File name : NiosII_top.v ***/

/*** Function : Main Processor of M-AGIC ***/

/*** Author : Y.M@rcie ***/

/*** History : Ver 1.0 2024/08/20 ***/

/*** ***/

/*** end of specifications ***/

/*** ***/

/*** Copyright (c) M@rcie. 2024. All rights reserved. ***/

/**************************************************************************/

module NiosII_top(

c2_out_clk_clk ,

c0_out_clk_clk ,

c1_out_clk_clk ,

clock_in_clk_in_clk ,

cpu1_smbus_avalon_slave_address ,

cpu1_smbus_avalon_slave_byteenable ,

cpu1_smbus_avalon_slave_chipselect ,

cpu1_smbus_avalon_slave_read ,

cpu1_smbus_avalon_slave_write ,

cpu1_smbus_avalon_slave_writedata ,

cpu1_smbus_avalon_slave_readdata ,

cpu1_smbus_avalon_slave_waitrequest ,

cpu1_smbus_interrupt_irq ,

cpu1_smbus_external_interface_acknowledge ,

cpu1_smbus_external_interface_irq ,

cpu1_smbus_external_interface_address ,

cpu1_smbus_external_interface_bus_enable ,

cpu1_smbus_external_interface_byte_enable ,

cpu1_smbus_external_interface_rw ,

cpu1_smbus_external_interface_write_data ,

cpu1_smbus_external_interface_read_data ,

emif_c10_0_oct_oct_rzqin ,

emif_c10_0_mem_mem_ck ,

emif_c10_0_mem_mem_ck_n ,

emif_c10_0_mem_mem_a ,

emif_c10_0_mem_mem_ba ,

emif_c10_0_mem_mem_cke ,

emif_c10_0_mem_mem_cs_n ,

emif_c10_0_mem_mem_odt ,

emif_c10_0_mem_mem_reset_n ,

emif_c10_0_mem_mem_we_n ,

emif_c10_0_mem_mem_ras_n ,

emif_c10_0_mem_mem_cas_n ,

emif_c10_0_mem_mem_dqs ,

emif_c10_0_mem_mem_dqs_n ,

emif_c10_0_mem_mem_dq ,

emif_c10_0_mem_mem_dm ,

emif_c10_0_status_local_cal_success ,

emif_c10_0_status_local_cal_fail ,

emif_c10_0_emif_usr_reset_n_reset_n ,

emif_c10_0_emif_usr_clk_clk ,

emif_c10_ddr3l_0_in_clk_clk ,

ext_irq1_in_export ,

ext_irq2_in_export ,

iopll_1_refclk_clk ,

iopll_1_locked_export ,

local_bus_bridge_out_expansion_board2_tcm_write_out ,

local_bus_bridge_out_expansion_board1_tcm_address_out ,

local_bus_bridge_out_expansion_board2_tcm_data_out ,

local_bus_bridge_out_fpga_knock_tcm_write_out ,

local_bus_bridge_out_expansion_board2_tcm_irq_in_in ,

local_bus_bridge_out_fpga_knock_tcm_data_out ,

local_bus_bridge_out_fpga_knock_tcm_irq_in_in ,

local_bus_bridge_out_expansion_board3_tcm_read_out ,

local_bus_bridge_out_expansion_board4_tcm_write_out ,

local_bus_bridge_out_expansion_board4_tcm_chipselect_out ,

local_bus_bridge_out_expansion_board1_tcm_data_out ,

local_bus_bridge_out_expansion_board4_tcm_irq_in_in ,

local_bus_bridge_out_expansion_board3_tcm_chipselect_out ,

local_bus_bridge_out_expansion_board4_tcm_address_out ,

local_bus_bridge_out_fpga_knock_tcm_chipselect_out ,

local_bus_bridge_out_expansion_board4_tcm_byteenable_out ,

local_bus_bridge_out_expansion_board1_tcm_write_out ,

local_bus_bridge_out_expansion_board4_tcm_data_out ,

local_bus_bridge_out_expansion_board2_tcm_read_out ,

local_bus_bridge_out_expansion_board3_tcm_byteenable_out ,

local_bus_bridge_out_expansion_board1_tcm_irq_in_in ,

local_bus_bridge_out_expansion_board2_tcm_chipselect_out ,

local_bus_bridge_out_fpga_knock_tcm_byteenable_out ,

local_bus_bridge_out_expansion_board2_tcm_byteenable_out ,

local_bus_bridge_out_expansion_board1_tcm_chipselect_out ,

local_bus_bridge_out_expansion_board3_tcm_address_out ,

local_bus_bridge_out_expansion_board3_tcm_write_out ,

local_bus_bridge_out_fpga_knock_tcm_read_out ,

local_bus_bridge_out_expansion_board1_tcm_byteenable_out ,

local_bus_bridge_out_expansion_board3_tcm_irq_in_in ,

local_bus_bridge_out_expansion_board3_tcm_data_out ,

local_bus_bridge_out_expansion_board1_tcm_read_out ,

local_bus_bridge_out_fpga_knock_tcm_waitrequest_in ,

local_bus_bridge_out_expansion_board2_tcm_address_out ,

local_bus_bridge_out_fpga_knock_tcm_address_out ,

local_bus_bridge_out_expansion_board4_tcm_read_out ,

lowvol_int_external_connection_export ,

qspi_flash_qspi_pins_dclk ,

qspi_flash_qspi_pins_ncs ,

qspi_flash_qspi_pins_data ,

testpin_sig_in_port ,

testpin_sig_out_port

);

////////////////////////////////////////////////////////////////////////////////

// Port Declarations

// input clk;

// input reset;

output c2_out_clk_clk ; // output, width = 1,

output c0_out_clk_clk ; // output, width = 1,

output c1_out_clk_clk ; // output, width = 1,

input clock_in_clk_in_clk ; // input, width = 1,

input [10:0] cpu1_smbus_avalon_slave_address ; // input, width = 11,

input [1:0] cpu1_smbus_avalon_slave_byteenable ; // input, width = 2,

input cpu1_smbus_avalon_slave_chipselect ; // input, width = 1,

input cpu1_smbus_avalon_slave_read ; // input, width = 1,

input cpu1_smbus_avalon_slave_write ; // input, width = 1,

input [15:0] cpu1_smbus_avalon_slave_writedata ; // input, width = 16,

output cpu1_smbus_avalon_slave_readdata ; // output, width = 16,

output cpu1_smbus_avalon_slave_waitrequest ; // output, width = 1,

output cpu1_smbus_interrupt_irq ; // output, width = 1,

input cpu1_smbus_external_interface_acknowledge ; // input, width = 1,

input cpu1_smbus_external_interface_irq ; // input, width = 1,

output [11:0] cpu1_smbus_external_interface_address ; // output, width = 12,

output cpu1_smbus_external_interface_bus_enable ; // output, width = 1,

output [1:0] cpu1_smbus_external_interface_byte_enable ; // output, width = 2,

output cpu1_smbus_external_interface_rw ; // output, width = 1,

output [15:0] cpu1_smbus_external_interface_write_data ; // output, width = 16,

input [15:0] cpu1_smbus_external_interface_read_data ; // input, width = 16,

input emif_c10_0_oct_oct_rzqin ; // input, width = 1,

output emif_c10_0_mem_mem_ck ; // output, width = 1,

output emif_c10_0_mem_mem_ck_n ; // output, width = 1,

output [14:0] emif_c10_0_mem_mem_a ; // output, width = 15,

output [2:0] emif_c10_0_mem_mem_ba ; // output, width = 3,

output emif_c10_0_mem_mem_cke ; // output, width = 1,

output emif_c10_0_mem_mem_cs_n ; // output, width = 1,

output emif_c10_0_mem_mem_odt ; // output, width = 1,

output emif_c10_0_mem_mem_reset_n ; // output, width = 1,

output emif_c10_0_mem_mem_we_n ; // output, width = 1,

output emif_c10_0_mem_mem_ras_n ; // output, width = 1,

output emif_c10_0_mem_mem_cas_n ; // output, width = 1,

inout [1:0] emif_c10_0_mem_mem_dqs ; // inout, width = 2,

inout [1:0] emif_c10_0_mem_mem_dqs_n ; // inout, width = 2,

inout [15:0] emif_c10_0_mem_mem_dq ; // inout, width = 16,

output [1:0] emif_c10_0_mem_mem_dm ; // output, width = 2,

output emif_c10_0_status_local_cal_success ; // output, width = 1,

output emif_c10_0_status_local_cal_fail ; // output, width = 1,

output emif_c10_0_emif_usr_reset_n_reset_n ; // output, width = 1,

output emif_c10_0_emif_usr_clk_clk ; // output, width = 1,

input emif_c10_ddr3l_0_in_clk_clk ; // input, width = 1,

input ext_irq1_in_export ; // input, width = 1,

input ext_irq2_in_export ; // input, width = 1,

input iopll_1_refclk_clk ; // input, width = 1,

output iopll_1_locked_export ; // output, width = 1,

output local_bus_bridge_out_expansion_board2_tcm_write_out ; // output, width = 1,

output [17:0] local_bus_bridge_out_expansion_board1_tcm_address_out ; // output, width = 18,

inout [31:0] local_bus_bridge_out_expansion_board2_tcm_data_out ; // inout, width = 32,

output local_bus_bridge_out_fpga_knock_tcm_write_out ; // output, width = 1,

input local_bus_bridge_out_expansion_board2_tcm_irq_in_in ; // input, width = 1,

inout [31:0] local_bus_bridge_out_fpga_knock_tcm_data_out ; // inout, width = 32,

input local_bus_bridge_out_fpga_knock_tcm_irq_in_in ; // input, width = 1,

output local_bus_bridge_out_expansion_board3_tcm_read_out ; // output, width = 1,

output local_bus_bridge_out_expansion_board4_tcm_write_out ; // output, width = 1,

output local_bus_bridge_out_expansion_board4_tcm_chipselect_out; // output, width = 1,

inout [31:0] local_bus_bridge_out_expansion_board1_tcm_data_out ; // inout, width = 32,

input local_bus_bridge_out_expansion_board4_tcm_irq_in_in ; // input, width = 1,

output local_bus_bridge_out_expansion_board3_tcm_chipselect_out; // output, width = 1,

output [17:0] local_bus_bridge_out_expansion_board4_tcm_address_out ; // output, width = 18,

output local_bus_bridge_out_fpga_knock_tcm_chipselect_out ; // output, width = 1,

output [3:0] local_bus_bridge_out_expansion_board4_tcm_byteenable_out; // output, width = 4,

output local_bus_bridge_out_expansion_board1_tcm_write_out ; // output, width = 1,

inout [31:0] local_bus_bridge_out_expansion_board4_tcm_data_out ; // inout, width = 32,

output local_bus_bridge_out_expansion_board2_tcm_read_out ; // output, width = 1,

output [3:0] local_bus_bridge_out_expansion_board3_tcm_byteenable_out; // output, width = 4,

input local_bus_bridge_out_expansion_board1_tcm_irq_in_in ; // input, width = 1,

output local_bus_bridge_out_expansion_board2_tcm_chipselect_out; // output, width = 1,

output [3:0] local_bus_bridge_out_fpga_knock_tcm_byteenable_out ; // output, width = 4,

output [3:0] local_bus_bridge_out_expansion_board2_tcm_byteenable_out; // output, width = 4,

output local_bus_bridge_out_expansion_board1_tcm_chipselect_out; // output, width = 1,

output [17:0] local_bus_bridge_out_expansion_board3_tcm_address_out ; // output, width = 18,

output local_bus_bridge_out_expansion_board3_tcm_write_out ; // output, width = 1,

output local_bus_bridge_out_fpga_knock_tcm_read_out ; // output, width = 1,

output [3:0] local_bus_bridge_out_expansion_board1_tcm_byteenable_out; // output, width = 4,

input local_bus_bridge_out_expansion_board3_tcm_irq_in_in ; // input, width = 1,

inout [31:0] local_bus_bridge_out_expansion_board3_tcm_data_out ; // inout, width = 32,

output local_bus_bridge_out_expansion_board1_tcm_read_out ; // output, width = 1,

input local_bus_bridge_out_fpga_knock_tcm_waitrequest_in ; // input, width = 1,

output [17:0] local_bus_bridge_out_expansion_board2_tcm_address_out ; // output, width = 18,

output [17:0] local_bus_bridge_out_fpga_knock_tcm_address_out ; // output, width = 18,

output local_bus_bridge_out_expansion_board4_tcm_read_out ; // output, width = 1,

input lowvol_int_external_connection_export ; // input, width = 1,

output qspi_flash_qspi_pins_dclk ; // output, width = 1,

output qspi_flash_qspi_pins_ncs ; // output, width = 1,

inout [3:0] qspi_flash_qspi_pins_data ; // inout, width = 4,

input [7:0] testpin_sig_in_port ; // input, width = 8,

output [7:0] testpin_sig_out_port ; // output, width = 8,

////////////////////////////////////////////////////////////////////////////////

// wire, reg, parameter Declarations

//none

////////////////////////////////////////////////////////////////////////////////

// Hardware Descriptions

M_AGIC_NiosII u0 (

.c2_out_clk_clk (c2_out_clk_clk), // output, width = 1, c2_out_clk.clk

.c0_out_clk_clk (c0_out_clk_clk), // output, width = 1, c0_out_clk.clk

.c1_out_clk_clk (c1_out_clk_clk), // output, width = 1, c1_out_clk.clk

.clock_in_clk_in_clk (clock_in_clk_in_clk), // input, width = 1, clock_in_clk_in.clk

.cpu1_smbus_avalon_slave_address (cpu1_smbus_avalon_slave_address), // input, width = 11, cpu1_smbus_avalon_slave.address

.cpu1_smbus_avalon_slave_byteenable (cpu1_smbus_avalon_slave_byteenable), // input, width = 2, .byteenable

.cpu1_smbus_avalon_slave_chipselect (cpu1_smbus_avalon_slave_chipselect), // input, width = 1, .chipselect

.cpu1_smbus_avalon_slave_read (cpu1_smbus_avalon_slave_read), // input, width = 1, .read

.cpu1_smbus_avalon_slave_write (cpu1_smbus_avalon_slave_write), // input, width = 1, .write

.cpu1_smbus_avalon_slave_writedata (cpu1_smbus_avalon_slave_writedata), // input, width = 16, .writedata

.cpu1_smbus_avalon_slave_readdata (cpu1_smbus_avalon_slave_readdata), // output, width = 16, .readdata

.cpu1_smbus_avalon_slave_waitrequest (cpu1_smbus_avalon_slave_waitrequest), // output, width = 1, .waitrequest

.cpu1_smbus_interrupt_irq (cpu1_smbus_interrupt_irq), // output, width = 1, cpu1_smbus_interrupt.irq

.cpu1_smbus_external_interface_acknowledge (cpu1_smbus_external_interface_acknowledge), // input, width = 1, cpu1_smbus_external_interface.acknowledge

.cpu1_smbus_external_interface_irq (cpu1_smbus_external_interface_irq), // input, width = 1, .irq

.cpu1_smbus_external_interface_address (cpu1_smbus_external_interface_address), // output, width = 12, .address

.cpu1_smbus_external_interface_bus_enable (cpu1_smbus_external_interface_bus_enable), // output, width = 1, .bus_enable

.cpu1_smbus_external_interface_byte_enable (cpu1_smbus_external_interface_byte_enable), // output, width = 2, .byte_enable

.cpu1_smbus_external_interface_rw (cpu1_smbus_external_interface_rw), // output, width = 1, .rw

.cpu1_smbus_external_interface_write_data (cpu1_smbus_external_interface_write_data), // output, width = 16, .write_data

.cpu1_smbus_external_interface_read_data (cpu1_smbus_external_interface_read_data), // input, width = 16, .read_data

.emif_c10_0_oct_oct_rzqin (emif_c10_0_oct_oct_rzqin), // input, width = 1, emif_c10_0_oct.oct_rzqin

.emif_c10_0_mem_mem_ck (emif_c10_0_mem_mem_ck), // output, width = 1, emif_c10_0_mem.mem_ck

.emif_c10_0_mem_mem_ck_n (emif_c10_0_mem_mem_ck_n), // output, width = 1, .mem_ck_n

.emif_c10_0_mem_mem_a (emif_c10_0_mem_mem_a), // output, width = 15, .mem_a

.emif_c10_0_mem_mem_ba (emif_c10_0_mem_mem_ba), // output, width = 3, .mem_ba

.emif_c10_0_mem_mem_cke (emif_c10_0_mem_mem_cke), // output, width = 1, .mem_cke

.emif_c10_0_mem_mem_cs_n (emif_c10_0_mem_mem_cs_n), // output, width = 1, .mem_cs_n

.emif_c10_0_mem_mem_odt (emif_c10_0_mem_mem_odt), // output, width = 1, .mem_odt

.emif_c10_0_mem_mem_reset_n (emif_c10_0_mem_mem_reset_n), // output, width = 1, .mem_reset_n

.emif_c10_0_mem_mem_we_n (emif_c10_0_mem_mem_we_n), // output, width = 1, .mem_we_n

.emif_c10_0_mem_mem_ras_n (emif_c10_0_mem_mem_ras_n), // output, width = 1, .mem_ras_n

.emif_c10_0_mem_mem_cas_n (emif_c10_0_mem_mem_cas_n), // output, width = 1, .mem_cas_n

.emif_c10_0_mem_mem_dqs (emif_c10_0_mem_mem_dqs), // inout, width = 2, .mem_dqs

.emif_c10_0_mem_mem_dqs_n (emif_c10_0_mem_mem_dqs_n), // inout, width = 2, .mem_dqs_n

.emif_c10_0_mem_mem_dq (emif_c10_0_mem_mem_dq), // inout, width = 16, .mem_dq

.emif_c10_0_mem_mem_dm (emif_c10_0_mem_mem_dm), // output, width = 2, .mem_dm

.emif_c10_0_status_local_cal_success (emif_c10_0_status_local_cal_success), // output, width = 1, emif_c10_0_status.local_cal_success

.emif_c10_0_status_local_cal_fail (emif_c10_0_status_local_cal_fail), // output, width = 1, .local_cal_fail

.emif_c10_0_emif_usr_reset_n_reset_n (emif_c10_0_emif_usr_reset_n_reset_n), // output, width = 1, emif_c10_0_emif_usr_reset_n.reset_n

.emif_c10_0_emif_usr_clk_clk (emif_c10_0_emif_usr_clk_clk), // output, width = 1, emif_c10_0_emif_usr_clk.clk

.emif_c10_ddr3l_0_in_clk_clk (emif_c10_ddr3l_0_in_clk_clk), // input, width = 1, emif_c10_ddr3l_0_in_clk.clk

.ext_irq1_in_export (ext_irq1_in_export), // input, width = 1, ext_irq1_in.export

.ext_irq2_in_export (ext_irq2_in_export), // input, width = 1, ext_irq2_in.export

.iopll_1_refclk_clk (iopll_1_refclk_clk), // input, width = 1, iopll_1_refclk.clk

.iopll_1_locked_export (iopll_1_locked_export), // output, width = 1, iopll_1_locked.export

.local_bus_bridge_out_expansion_board2_tcm_write_out (local_bus_bridge_out_expansion_board2_tcm_write_out), // output, width = 1, local_bus_bridge_out.expansion_board2_tcm_write_out

.local_bus_bridge_out_expansion_board1_tcm_address_out (local_bus_bridge_out_expansion_board1_tcm_address_out), // output, width = 18, .expansion_board1_tcm_address_out

.local_bus_bridge_out_expansion_board2_tcm_data_out (local_bus_bridge_out_expansion_board2_tcm_data_out), // inout, width = 32, .expansion_board2_tcm_data_out

.local_bus_bridge_out_fpga_knock_tcm_write_out (local_bus_bridge_out_fpga_knock_tcm_write_out), // output, width = 1, .fpga_knock_tcm_write_out

.local_bus_bridge_out_expansion_board2_tcm_irq_in_in (local_bus_bridge_out_expansion_board2_tcm_irq_in_in), // input, width = 1, .expansion_board2_tcm_irq_in_in

.local_bus_bridge_out_fpga_knock_tcm_data_out (local_bus_bridge_out_fpga_knock_tcm_data_out), // inout, width = 32, .fpga_knock_tcm_data_out

.local_bus_bridge_out_fpga_knock_tcm_irq_in_in (local_bus_bridge_out_fpga_knock_tcm_irq_in_in), // input, width = 1, .fpga_knock_tcm_irq_in_in

.local_bus_bridge_out_expansion_board3_tcm_read_out (local_bus_bridge_out_expansion_board3_tcm_read_out), // output, width = 1, .expansion_board3_tcm_read_out

.local_bus_bridge_out_expansion_board4_tcm_write_out (local_bus_bridge_out_expansion_board4_tcm_write_out), // output, width = 1, .expansion_board4_tcm_write_out

.local_bus_bridge_out_expansion_board4_tcm_chipselect_out (local_bus_bridge_out_expansion_board4_tcm_chipselect_out), // output, width = 1, .expansion_board4_tcm_chipselect_out

.local_bus_bridge_out_expansion_board1_tcm_data_out (local_bus_bridge_out_expansion_board1_tcm_data_out), // inout, width = 32, .expansion_board1_tcm_data_out

.local_bus_bridge_out_expansion_board4_tcm_irq_in_in (local_bus_bridge_out_expansion_board4_tcm_irq_in_in), // input, width = 1, .expansion_board4_tcm_irq_in_in

.local_bus_bridge_out_expansion_board3_tcm_chipselect_out (local_bus_bridge_out_expansion_board3_tcm_chipselect_out), // output, width = 1, .expansion_board3_tcm_chipselect_out

.local_bus_bridge_out_expansion_board4_tcm_address_out (local_bus_bridge_out_expansion_board4_tcm_address_out), // output, width = 18, .expansion_board4_tcm_address_out

.local_bus_bridge_out_fpga_knock_tcm_chipselect_out (local_bus_bridge_out_fpga_knock_tcm_chipselect_out), // output, width = 1, .fpga_knock_tcm_chipselect_out

.local_bus_bridge_out_expansion_board4_tcm_byteenable_out (local_bus_bridge_out_expansion_board4_tcm_byteenable_out), // output, width = 4, .expansion_board4_tcm_byteenable_out

.local_bus_bridge_out_expansion_board1_tcm_write_out (local_bus_bridge_out_expansion_board1_tcm_write_out), // output, width = 1, .expansion_board1_tcm_write_out

.local_bus_bridge_out_expansion_board4_tcm_data_out (local_bus_bridge_out_expansion_board4_tcm_data_out), // inout, width = 32, .expansion_board4_tcm_data_out

.local_bus_bridge_out_expansion_board2_tcm_read_out (local_bus_bridge_out_expansion_board2_tcm_read_out), // output, width = 1, .expansion_board2_tcm_read_out

.local_bus_bridge_out_expansion_board3_tcm_byteenable_out (local_bus_bridge_out_expansion_board3_tcm_byteenable_out), // output, width = 4, .expansion_board3_tcm_byteenable_out

.local_bus_bridge_out_expansion_board1_tcm_irq_in_in (local_bus_bridge_out_expansion_board1_tcm_irq_in_in), // input, width = 1, .expansion_board1_tcm_irq_in_in

.local_bus_bridge_out_expansion_board2_tcm_chipselect_out (local_bus_bridge_out_expansion_board2_tcm_chipselect_out), // output, width = 1, .expansion_board2_tcm_chipselect_out

.local_bus_bridge_out_fpga_knock_tcm_byteenable_out (local_bus_bridge_out_fpga_knock_tcm_byteenable_out), // output, width = 4, .fpga_knock_tcm_byteenable_out

.local_bus_bridge_out_expansion_board2_tcm_byteenable_out (local_bus_bridge_out_expansion_board2_tcm_byteenable_out), // output, width = 4, .expansion_board2_tcm_byteenable_out

.local_bus_bridge_out_expansion_board1_tcm_chipselect_out (local_bus_bridge_out_expansion_board1_tcm_chipselect_out), // output, width = 1, .expansion_board1_tcm_chipselect_out

.local_bus_bridge_out_expansion_board3_tcm_address_out (local_bus_bridge_out_expansion_board3_tcm_address_out), // output, width = 18, .expansion_board3_tcm_address_out

.local_bus_bridge_out_expansion_board3_tcm_write_out (local_bus_bridge_out_expansion_board3_tcm_write_out), // output, width = 1, .expansion_board3_tcm_write_out

.local_bus_bridge_out_fpga_knock_tcm_read_out (local_bus_bridge_out_fpga_knock_tcm_read_out), // output, width = 1, .fpga_knock_tcm_read_out

.local_bus_bridge_out_expansion_board1_tcm_byteenable_out (local_bus_bridge_out_expansion_board1_tcm_byteenable_out), // output, width = 4, .expansion_board1_tcm_byteenable_out

.local_bus_bridge_out_expansion_board3_tcm_irq_in_in (local_bus_bridge_out_expansion_board3_tcm_irq_in_in), // input, width = 1, .expansion_board3_tcm_irq_in_in

.local_bus_bridge_out_expansion_board3_tcm_data_out (local_bus_bridge_out_expansion_board3_tcm_data_out), // inout, width = 32, .expansion_board3_tcm_data_out

.local_bus_bridge_out_expansion_board1_tcm_read_out (local_bus_bridge_out_expansion_board1_tcm_read_out), // output, width = 1, .expansion_board1_tcm_read_out

.local_bus_bridge_out_fpga_knock_tcm_waitrequest_in (local_bus_bridge_out_fpga_knock_tcm_waitrequest_in), // input, width = 1, .fpga_knock_tcm_waitrequest_in

.local_bus_bridge_out_expansion_board2_tcm_address_out (local_bus_bridge_out_expansion_board2_tcm_address_out), // output, width = 18, .expansion_board2_tcm_address_out

.local_bus_bridge_out_fpga_knock_tcm_address_out (local_bus_bridge_out_fpga_knock_tcm_address_out), // output, width = 18, .fpga_knock_tcm_address_out

.local_bus_bridge_out_expansion_board4_tcm_read_out (local_bus_bridge_out_expansion_board4_tcm_read_out), // output, width = 1, .expansion_board4_tcm_read_out

.lowvol_int_external_connection_export (lowvol_int_external_connection_export), // input, width = 1, lowvol_int_external_connection.export

.qspi_flash_qspi_pins_dclk (qspi_flash_qspi_pins_dclk), // output, width = 1, qspi_flash_qspi_pins.dclk

.qspi_flash_qspi_pins_ncs (qspi_flash_qspi_pins_ncs), // output, width = 1, .ncs

.qspi_flash_qspi_pins_data (qspi_flash_qspi_pins_data), // inout, width = 4, .data

.testpin_sig_in_port (testpin_sig_in_port), // input, width = 8, testpin_sig.in_port

.testpin_sig_out_port (testpin_sig_out_port) // output, width = 8, .out_port

);

endmodule

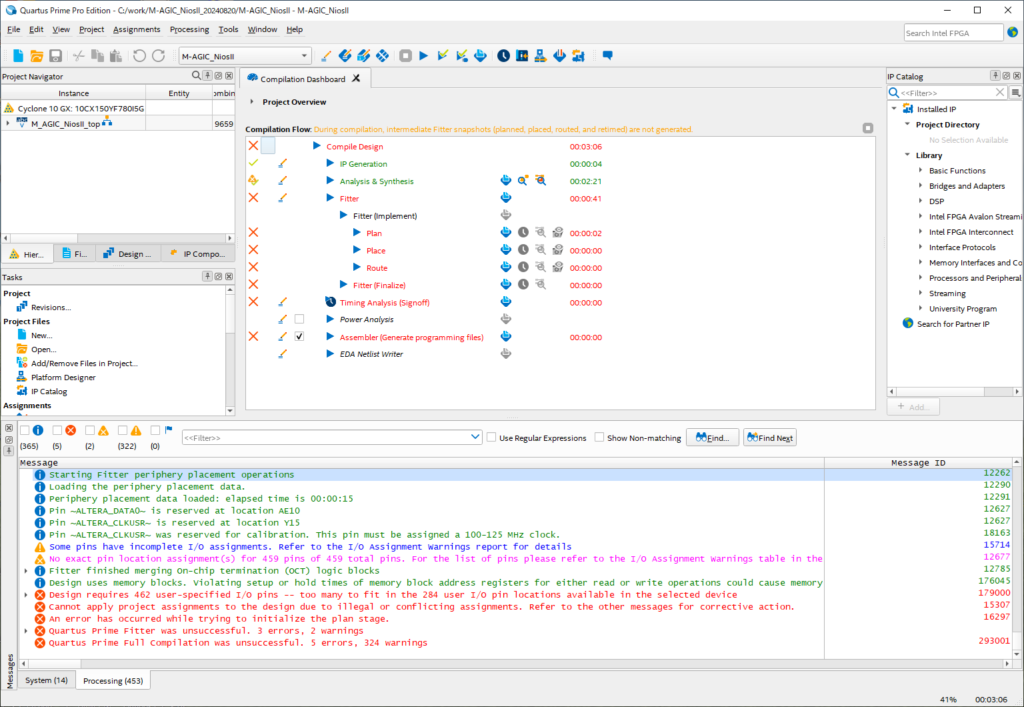

↓コンパイル後、エラーはなくなった??けど、、

Error(179000): Design requires 462 user-specified I/O pins — too many to fit in the 284 user I/O pin locations available in the selected device

Info(179001): Current design requires 462 user-specified I/O pins — 462 normal user-specified I/O pins and 0 programming pins that have been constrained to use dual-purpose I/O pin locations

Info(179002): Targeted device has 284 I/O pin locations available for user I/O — 240 general-purpose I/O pins and 44 dual-purpose I/O pins

今度はえいやっ!っと全部出してたピンが大杉って怒られてますね。当たり前かw。

こうやって時間が解けていくんですよね。。。馬鹿だおれ。

どーすっかな。ゴリゴリレジスタでも書いて突っ込むかな。

以上